# **Specification for Approval**

PRODUCT NAME: RGS15128128FH035 PRODUCT NO.: 9923901000

|       | CUSTOMER    |  |

|-------|-------------|--|

|       |             |  |

|       |             |  |

|       |             |  |

|       | APPROVED BY |  |

|       | APPROVED BY |  |

|       |             |  |

|       |             |  |

|       |             |  |

|       |             |  |

| DATE: |             |  |

RITDISPLAY CORP. APPROVED

## **REVISION RECORD**

| REV. | REVISION DESCRIPTION                                                                                                             | REV. DATE REMARK |               |  |  |  |

|------|----------------------------------------------------------------------------------------------------------------------------------|------------------|---------------|--|--|--|

| X01  | INITIAL RELEASE                                                                                                                  | 2009. 03. 16     |               |  |  |  |

| X02  | <ul><li>Modify luminance specifications</li><li>Add the panel electrical specifications</li></ul>                                | 2009. 07. 02     | Page 6, 7 & 8 |  |  |  |

| A01  | <ul> <li>Transfer from X version</li> <li>Add the information of module weight</li> <li>Add the packing specification</li> </ul> | 2009. 07. 24     | Page 5 & 17   |  |  |  |

| A02  | ■ Modify seal color (white→black)                                                                                                | 2009. 12. 31     | Page 16       |  |  |  |

| A03  | <ul> <li>Add appendix of precautions for using<br/>the OLED module</li> </ul>                                                    | 2014. 03. 31     | Page 22~31    |  |  |  |

## **CONTENTS**

| ITEM                                             | <b>PAGE</b> |

|--------------------------------------------------|-------------|

| 1. SCOPE                                         | 4           |

| 2. WARRANTY                                      | 4           |

| 3. FEATURES                                      | 4           |

| 4. MECHANICAL DATA                               | 5           |

| 5. MAXIMUM RATINGS                               | 6           |

| 6. ELECTRICAL CHARACTERISTICS                    | 8           |

| 6.1 D.C ELECTRICAL CHARACTERISTICS               |             |

| 6.2 ELECTRO-OPTICAL CHARACTERISTICS              |             |

| 7. INTERFACE                                     | 9           |

| 7.1 FUNCTION BLOCK DIAGRAM                       |             |

| 7.2 PANEL LAYOUT DIAGRAM                         |             |

| 7.3 PIN ASSIGNMENTS                              |             |

| 7.4 GRAPHIC DISPLAY DATA RAM ADDRESS MAP         |             |

| 7.5 INTERFACE TIMING CHART                       |             |

| 8. POWER ON / OFF SEQUENCE & APPLICATION CIRCUIT | 13          |

| 8.1 POWER ON / OFF SEQUENCE                      |             |

| 8.2 APPLICATION CIRCUIT                          |             |

| 8.3 COMMAND TABLE                                |             |

| 9. RELIABILITY TEST CONDITIONS                   | 15          |

| 10. EXTERNAL DIMENSION                           | 16          |

| 11. PACKING SPECIFICATION                        | 17          |

| 12. APPENDIXES                                   | 18          |

## 1. SCOPE

The purpose of this specification is to define the general provisions and quality requirements that apply to the supply of display cells manufactured by RiTdisplay. This document, together with the Module Ass'y Drawing, is the highest-level specification for this product. It describes the product, identifies supporting documents and contains specifications.

## 2. WARRANTY

RiTdisplay warrants that the products delivered pursuant to this specification (or order) will conform to the agreed specifications for twelve (12) months from the shipping date ("Warranty Period"). RiTdisplay is obligated to repair or replace the products which are found to be defective or inconsistent with the specifications during the Warranty Period without charge, on condition that the products are stored or used as the conditions specified in the specifications. Nevertheless, RiTdisplay is not obligated to repair or replace the products without charge if the defects or inconsistency are caused by the force majeure or the reckless behaviors of the customer.

After the Warranty Period, all repairs or replacements of the products are subject to charge.

## 3. FEATURES

- Small molecular organic light emitting diode.

- Color: 262K color and 65K colors

- Panel matrix : 128\*128Driver IC : SSD1351

- Excellent quick response time.

- Extremely thin thickness for best mechanism design: 1.61mm

- High contrast : 2000:1

- Wide viewing angle: 160°

- Strong environmental resistance.

- 8/16/18-bit 6800-series Parallel Interface, 8/16/18-bit 8080-series Parallel Interface, Serial Peripheral Interface.

- Wide range of operating temperature : -40 to 70 ℃.

- Anti-glare polarizer.

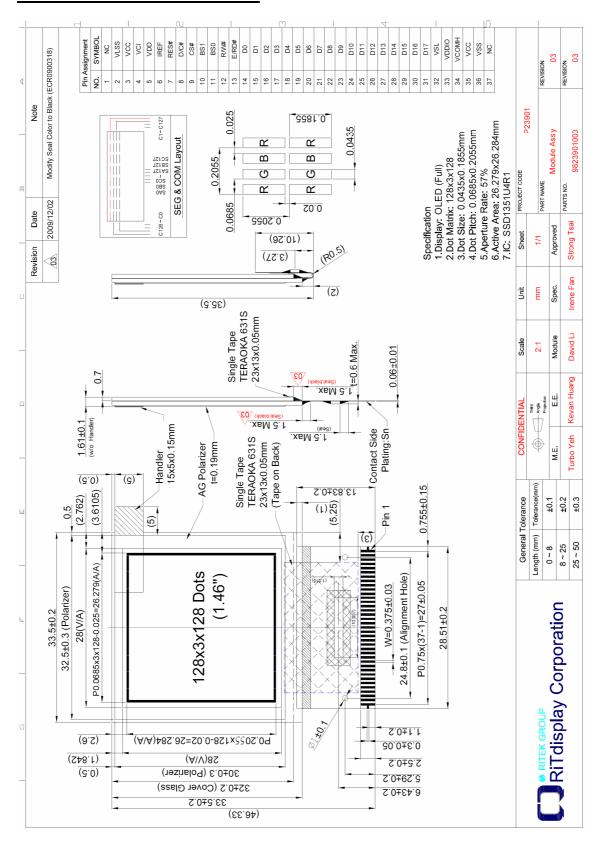

## **4. MECHANICAL DATA**

| NO | ITEM              | SPECIFICATION                   | UNIT            |

|----|-------------------|---------------------------------|-----------------|

| 1  | Dot Matrix        | 128 (W) x (RxGxB) x 128 (H)     | dot             |

| 2  | Dot Size          | 0.0435 (W) x 0.1855 (H)         | mm <sup>2</sup> |

| 3  | Dot Pitch         | 0.0685 (W) x 0.2055 (H)         | mm <sup>2</sup> |

| 4  | Aperture Rate     | 57                              | %               |

| 5  | Active Area       | 26.279 (W) x 26.284 (H)         | mm <sup>2</sup> |

| 6  | Panel Size        | 33.5 (W) x 33.5 (H)             | mm <sup>2</sup> |

| 7* | Panel Thickness   | 1.42 ± 0.1                      | mm              |

| 8  | Module Size       | 33.5 (W) x 46.33 (H) x 1.61 (D) | mm <sup>3</sup> |

| 9  | Diagonal A/A size | 1.46                            | inch            |

| 10 | Module Weight     | 3.93 ± 10%                      | gram            |

<sup>\*</sup> Panel thickness includes substrate glass, cover glass and UV glue thickness.

## **5. MAXIMUM RATINGS**

| ITEM                              | MIN    | MAX      | UNIT | Condition                  | Remark            |

|-----------------------------------|--------|----------|------|----------------------------|-------------------|

| Supply Voltage (V <sub>CI</sub> ) | -0.3   | 4        | V    | Ta = 25 ℃                  | IC maximum rating |

| Supply Voltage (Vcc)              | 10     | 19       | V    | Ta = 25℃                   | IC maximum rating |

| Supply Voltage (VDDIO)            | -0.5   | $V_{CI}$ | V    | Ta = 25℃                   | IC maximum rating |

| Operating Temp.                   | -40    | 70       | °C   |                            |                   |

| Storage Temp                      | -40    | 85       | °C   |                            |                   |

| Humidity                          | -      | 85       | %    |                            |                   |

| Life Time                         | 11,000 | -        | Hrs  | 90 cd/m², 50% checkerboard | Note (1)          |

| Life Time                         | 14,000 | -        | Hrs  | 70 cd/m², 50% checkerboard | Note (2)          |

## Note:

- (A) Under Vcc = 16.5V,  $Ta = 25 \,^{\circ}\text{C}$ , 50% RH.

- (B) Life time is defined the amount of time when the luminance has decayed to less than 50% of the initial measured luminance.

## (1) Setting of 90 cd/m<sup>2</sup>:

Master contrast setting: 0x0B

Red contrast setting: 0x70

Green contrast setting: 0x71

Blue contrast setting: 0x94

Frame rate: 105HzDuty setting: 1/128

## (2) Setting of 70 cd/m<sup>2</sup>:

Master contrast setting: 0x09

Red contrast setting: 0x66

Green contrast setting: 0x6A

Blue contrast setting: 0x89

Frame rate: 105HzDuty setting: 1/128

## **6. ELECTRICAL CHARACTERISTICS**

## **6.1 D.C ELECTRICAL CHARACTERISTICS**

| SYMBOL            | PARAMETERS                                                                                                 | TEST<br>CONDITION      | MIN                       | TYP  | MAX                       | UNIT |

|-------------------|------------------------------------------------------------------------------------------------------------|------------------------|---------------------------|------|---------------------------|------|

| V <sub>CC</sub>   | Analog power supply (for OLED panel)                                                                       |                        | 16                        | 16.5 | 17                        | V    |

| $V_{CI}$          | Digital power supply                                                                                       |                        | 2.4                       | 2.8  | 3.5                       | V    |

| $V_{DDIO}$        | I/O voltage power supply                                                                                   |                        | 1.65                      | -    | $V_{CI}$                  | V    |

| I <sub>DD</sub>   | $V_{CI} = V_{DDIO} = 3.5V$ , $V_{CC} = 1$<br>External $V_{DD} = 2.6V$ , Displ<br>No panel attached, contra | ay ON,                 |                           | 170  | 190                       | uA   |

| I <sub>DDIO</sub> | $V_{CI} = V_{DDIO} =$ , 3.5V, $V_{CC} = 16V$ , Display ON,                                                 | External VDD<br>= 2.6V |                           | 0.5  | 10                        | uA   |

| סוטטי             | No panel attached, contrast = FF                                                                           | Internal VDD           |                           | 0.5  | 10                        | uA   |

| I <sub>Cl</sub>   | $V_{CI} = V_{DDIO} =$ , 3.5V,<br>$V_{CC} = 16V$ , Display ON,                                              | External VDD<br>= 2.6V | -                         | 60   | 70                        | uA   |

| iCl               | No panel attached, contrast = FF                                                                           | Internal VDD           |                           | 255  | 280                       | uA   |

| I <sub>CC</sub>   | $V_{CI} = V_{DDIO} =$ , 3.5V, $V_{CC} = 16V$ , Display ON,                                                 | External VDD<br>= 2.6V | -                         | 1.15 | 1.26                      | mA   |

| icc               | No panel attached, contrast = FF                                                                           | Internal VDD           |                           | 1.15 | 1.26                      | mA   |

| $V_{IH}$          | Hi logic input level                                                                                       |                        | 0.8*<br>V <sub>DDIO</sub> | -    | $V_{DDIO}$                | V    |

| $V_{IL}$          | Low logic input level                                                                                      |                        | 0                         | -    | 0.2*<br>V <sub>DDIO</sub> | V    |

| $V_{OH}$          | Hi logic output level                                                                                      |                        | 0.9*<br>V <sub>DDIO</sub> | -    | $V_{DDIO}$                | V    |

| V <sub>OL</sub>   | Low logic output level                                                                                     |                        | 0                         | -    | 0.1*<br>V <sub>DDIO</sub> | V    |

|                   | Segment Output Current                                                                                     | Contrast=FF            | -                         | 200  | -                         | uA   |

| I <sub>SEG</sub>  | Setting V <sub>CC</sub> = 16V at IREF =                                                                    | Contrast=7F            | -                         | 100  | -                         | uA   |

|                   | 12.5uA                                                                                                     | Contrast=3F            | -                         | 50   | -                         | uA   |

- 7 - REV.: A03 2014/03/31

## **6.2 ELECTRO-OPTICAL CHARACTERISTICS**

## PANEL ELECTRICAL SPECIFICATIONS

| PARAMETER                      | MIN    | TYP. | MAX  | UNITS             | COMMENTS                       |

|--------------------------------|--------|------|------|-------------------|--------------------------------|

| Normal mode current            |        | 30   | 32   | mA                | All pixels on (1)              |

| Standby mode current           |        | 3    | 4    | mA                | Standby mode 10% pixels on (2) |

| Normal mode power consumption  |        | 495  | 528  | mW                | All pixels on (1)              |

| Standby mode power consumption |        | 49.5 | 66   | mW                | Standby mode 10% pixels on (2) |

| Normal mode<br>Luminance       | 70     | 90   |      | cd/m <sup>2</sup> | Display Average                |

| Standby mode<br>Luminance      |        | 20   |      | cd/m <sup>2</sup> |                                |

| CIEx (White)                   | 0.24   | 0.28 | 0.32 |                   |                                |

| CIEy (White)                   | 0.28   | 0.32 | 0.36 |                   |                                |

| CIEx (Red)                     | 0.62   | 0.66 | 0.70 |                   |                                |

| CIEy (Red)                     | 0.29   | 0.33 | 0.37 |                   | v v (CIE 1021)                 |

| CIEx (Green)                   | 0.26   | 0.30 | 0.34 |                   | x, y (CIE 1931)                |

| CIEy (Green)                   | 0.59   | 0.63 | 0.67 |                   |                                |

| CIEx (Blue)                    | 0.10   | 0.14 | 0.18 |                   |                                |

| CIEy (Blue)                    | 0.14   | 0.18 | 0.22 |                   |                                |

| Dark Room Contrast             | 2000:1 |      |      |                   |                                |

| Viewing Angle                  | 160    | ·    |      | degree            | _                              |

| Response Time                  |        | 10   |      | μs                |                                |

## (1) Normal mode condition:

Driving Voltage: 16.5V

Master contrast setting : 0x0BRed contrast setting : 0x70

Green contrast setting : 0x71Blue contrast setting : 0x94

Frame rate: 105HzDuty setting: 1/128

## (2) Standby mode condition:

Driving Voltage: 16.5V

- Master contrast setting: 0x04

Red contrast setting : 0x4EGreen contrast setting : 0x53

- Blue contrast setting : 0X6E

Frame rate: 105HzDuty setting: 1/128

## 7. INTERFACE

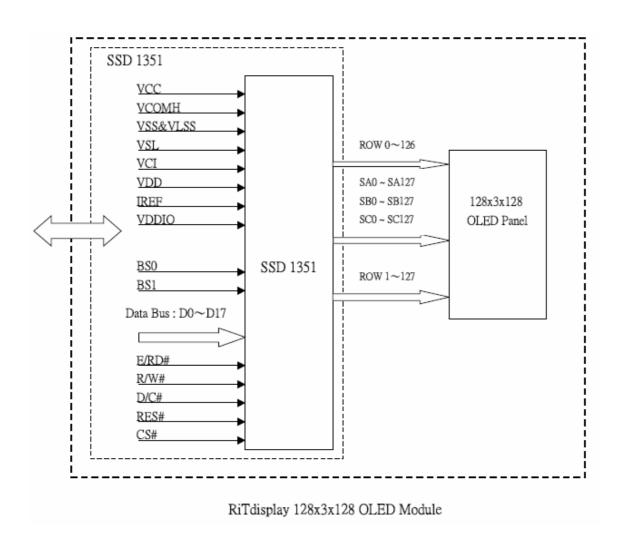

## 7.1 FUNCTION BLOCK DIAGRAM

## 7.2 PANEL LAYOUT DIAGRAM

- 9 - REV.: A03 2014/03/31

## 7.3 PIN ASSIGNMENTS

| PIN NAME | PIN NO | DESCRIPTION                                                                                   |

|----------|--------|-----------------------------------------------------------------------------------------------|

| NC       | 1      | No connection.                                                                                |

| VLSS     | 2      | Analog system ground pin                                                                      |

| VCC      | 3      | Power supply for panel driving voltage.                                                       |

| VCI      | 4      | Digital voltage power supply.                                                                 |

| VDD      | 5      | Power supply pin for core logic operation.                                                    |

| IREF     | 6      | A resistor should be connected between this pin and VSS.                                      |

| RES#     | 7      | Hardware Reset pin (Low active).                                                              |

| D/C#     | 8      | H: Data, L: Command.                                                                          |

| CS#      | 9      | Chip select pin.                                                                              |

| BS1      | 10     | Interface select pin.                                                                         |

| BS0      | 11     | Interface select pin.                                                                         |

| R/W#     | 12     | 8080: data write enable pin; 6800:Read/Write select pin.                                      |

| E/RD#    | 13     | 8080: data read enable pin; 6800:Read/Write enable pin.                                       |

| D0       | 14     |                                                                                               |

| D1       | 15     |                                                                                               |

| D2       | 16     |                                                                                               |

| D3       | 17     |                                                                                               |

| D4       | 18     |                                                                                               |

| D5       | 19     |                                                                                               |

| D6       | 20     |                                                                                               |

| D7       | 21     |                                                                                               |

| D8       | 22     | These pins are bi-directional data bus connecting to the                                      |

| D9       | 23     | MCU data bus.                                                                                 |

| D10      | 24     |                                                                                               |

| D11      | 25     |                                                                                               |

| D12      | 26     |                                                                                               |

| D13      | 27     |                                                                                               |

| D14      | 28     |                                                                                               |

| D15      | 29     |                                                                                               |

| D16      | 30     |                                                                                               |

| D17      | 31     |                                                                                               |

| VSL      | 32     | This is segment voltage reference pin.                                                        |

| VDDIO    | 33     | Power supply for interface logic level.                                                       |

| VCOMH    | 34     | COM signal deselected voltage level. A capacitor should be connected between this pin an VSS. |

| VCC      | 35     | Power supply for panel driving voltage.                                                       |

| VSS      | 36     | Ground.                                                                                       |

| NC       | 37     | No connection.                                                                                |

## 7.4 GRAPHIC DISPLAY DATA RAM ADDRESS MAP

The GDDRAM is a bit mapped static RAM holding the pattern to be displayed. The RAM size is 128 x 128 x 18bits. For mechanical flexibility, re-mapping on both Segment and Common outputs can be selected by software. Each pixel has 18-bit data. Each sub-pixels for color A, B and C have 6 bits. The arrangement of data pixel in graphic display data RAM is shown below.

| 262k Color Depth Graphic Display Data RAM Structure |          |     |       |          |            |      |     |     |      |       |       |       |       |        |

|-----------------------------------------------------|----------|-----|-------|----------|------------|------|-----|-----|------|-------|-------|-------|-------|--------|

| Segment                                             | Normal   |     | 0     |          |            | 1    |     | 2   | <br> | 126   |       | 127   |       |        |

| Address                                             | Remapped |     | . 127 |          |            | 126  |     | 125 | <br> | 1     |       | 0     |       |        |

| C                                                   | olor     | A   | В     | С        | A          | В    | С   | Α   |      | C     | A     | В     | C     |        |

|                                                     | Data     | A5  | B5    | C5       | A5         | B5   | C5  | A5  | <br> | C5    | A5    | B5    | C5    |        |

| I                                                   | Format   | A4  | B4    | C4       | A4         | B4   | C4  | A4  | <br> | C4    | A4    | B4    | C4    |        |

|                                                     |          | A3  | B3    | C3       | A3         | B3   | C3  | A3  | <br> | C3    | A3    | В3    | C3    |        |

| Common                                              |          | A2  | B2    | C2       | A2         | B2   | C2  | A2  | <br> | C2    | A2    | B2    | C2    |        |

| Address                                             |          | A1  | B1    | C1       | A1         | B1   | C1  | A1  | <br> | C1    | A1    | B1    | C1    |        |

|                                                     |          | A0  | B0    | C0       | A0         | B0   | C0  | A0  | <br> | C0    | A0    | B0    | C0    | Common |

| Normal                                              | Remapped |     |       |          |            |      |     |     |      |       |       |       |       | output |

| 0                                                   | 127      | 6   | 6     | 6        | 6          | 6    | 6   | 6   | <br> | 6     | 6     | 6     | 6     | COM0   |

| 1                                                   | 126      | 6   | 6     | 6        | 6          | 6    | 6   | 6   | <br> | 6     | 6     | 6     | 6     | COM1   |

| 2                                                   | 125      | 6   | 6     | 6        | 6          | 6    | 6   | 6   | <br> | 6     | 6     | 6     | 6     | COM2   |

| 3                                                   | 124      | 6   | V     | 6        | 6          | 6    | 6   | 6   | <br> | 6     | 6     | 6     | 6     | COM3   |

| 4                                                   | 123      | 6   | 6     | 6        | 6          | 6    | 6   | 6   | <br> | 6     | 6     | 6     | 6     | COM4   |

| 5                                                   | 122      | 6   | 6     | 6        | 6          | 6    | 6   | 6   | <br> | 6     | 6     | 6     | 6     | COM5   |

| 6                                                   | 121      | 6   | 6     | no of bi | ts in this | cell | 6   | 6   | <br> | 6     | 6     | 6     | 6     | COM6   |

| 7                                                   | 120      |     |       |          |            |      |     |     | <br> | 6     | 6     | 6     | 6     | COM7   |

| :                                                   | :        | :   | :     | :        | :          | :    | :   | :   | <br> | :     | :     | :     | :     | :      |

| :                                                   | :        | :   | :     | :        | :          | :    | :   | :   | <br> | :     | :     | :     | :     | :      |

| :                                                   | :        | :   | :     | :        | :          | :    | :   | :   | <br> | :     | :     | :     | :     | :      |

| 123                                                 | 4        | 6   | 6     | 6        | 6          | 6    | 6   | 6   | <br> | 6     | 6     | 6     | 6     | :      |

| 124                                                 | 3        | 6   | 6     | 6        | 6          | 6    | 6   | 6   | <br> | 6     | 6     | 6     | 6     | COM124 |

| 125                                                 | 2        | 6   | 6     | 6        | 6          | 6    | 6   | 6   | <br> | 6     | 6     | 6     | 6     | COM125 |

| 126                                                 | 1        | 6   | 6     | 6        | 6          | 6    | 6   | 6   | <br> | 6     | 6     | 6     | 6     | COM126 |

| 127                                                 | 0        | 6   | 6     | 6        | 6          | 6    | 6   | 6   | <br> | 6     | 6     | 6     | 6     | COM127 |

|                                                     |          |     | •     |          |            |      |     |     |      |       |       |       |       |        |

| SEG                                                 | output   | SA0 | SB0   | SC0      | SA1        | SB1  | SC1 | SA2 | <br> | SC126 | SA127 | SB127 | SC127 |        |

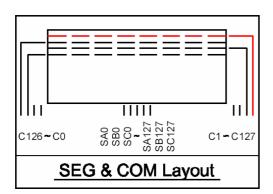

## 7.5 INTERFACE TIMING CHART

|                                    | 8080-Series MCU Parallel Interface Timing Characteristics                            |     |     |     |      |  |  |  |  |  |

|------------------------------------|--------------------------------------------------------------------------------------|-----|-----|-----|------|--|--|--|--|--|

| (V <sub>DD</sub> - V <sub>SS</sub> | $V_{DD}$ - $V_{SS}$ = 2.4 to 2.6V, $V_{DDIO}$ =1.65V, $V_{CI}$ = 2.8V, $T_A$ = 25°C) |     |     |     |      |  |  |  |  |  |

| Symbol                             | Parameter                                                                            | Min | Тур | Max | Unit |  |  |  |  |  |

| t <sub>CYCLE</sub>                 | Clock Cycle Time                                                                     | 300 | -   | -   | ns   |  |  |  |  |  |

| t <sub>AS</sub>                    | Address Setup Time                                                                   | 10  | -   | -   | ns   |  |  |  |  |  |

| t <sub>AH</sub>                    | Address Hold Time                                                                    | 0   | -   | -   | ns   |  |  |  |  |  |

| $t_{DSW}$                          | Write Data Setup Time                                                                | 40  | -   | -   | ns   |  |  |  |  |  |

| $t_{\mathrm{DHW}}$                 | Write Data Hold Time                                                                 | 7   | -   | -   | ns   |  |  |  |  |  |

| t <sub>DHR</sub>                   | Read Data Hold Time                                                                  | 20  | -   | -   | ns   |  |  |  |  |  |

| t <sub>OH</sub>                    | Output Disable Time                                                                  | -   | -   | 70  | ns   |  |  |  |  |  |

| t <sub>ACC</sub>                   | Access Time                                                                          | -   | -   | 140 | ns   |  |  |  |  |  |

| t <sub>PWLR</sub>                  | Read Low Time                                                                        | 150 | -   | -   | ns   |  |  |  |  |  |

| $t_{PWLW}$                         | Write Low Time                                                                       | 60  | -   | -   | ns   |  |  |  |  |  |

| t <sub>PWHR</sub>                  | Read High Time                                                                       | 60  | -   | -   | ns   |  |  |  |  |  |

| t <sub>PWHW</sub>                  | Write High Time                                                                      | 60  | -   | -   | ns   |  |  |  |  |  |

| t <sub>R</sub>                     | Rise Time                                                                            | -   | -   | 15  | ns   |  |  |  |  |  |

| t <sub>F</sub>                     | Fall Time                                                                            | -   | -   | 15  | ns   |  |  |  |  |  |

| t <sub>CS</sub>                    | Chip select setup time                                                               | 0   | -   | -   | ns   |  |  |  |  |  |

| t <sub>CSH</sub>                   | Chip select hold time to read signal                                                 | 0   | -   | -   | ns   |  |  |  |  |  |

| t <sub>CSF</sub>                   | Chip select hold time                                                                | 20  | -   | -   | ns   |  |  |  |  |  |

### 8080-series MCU parallel interface characteristics

## **Note**

(1) when 8 bit used: D[7:0] instead; when 16 bit used: [15:0] instead; when 18 bit used: D[17:0] instead.

- 12 - REV.: A03 2014/03/31

## 8. POWER ON / OFF SEQUENCE & APPLICATION CIRCUIT

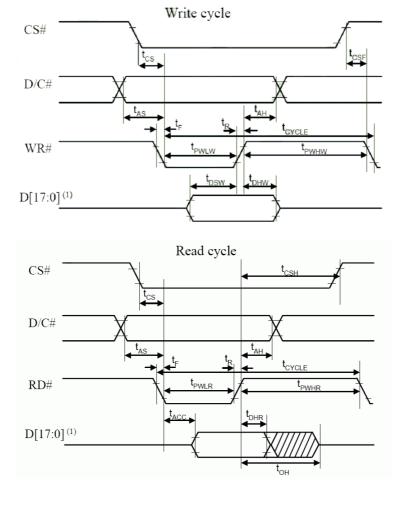

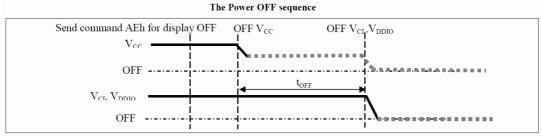

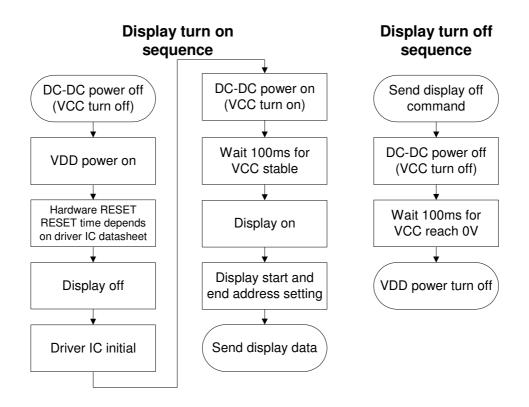

### 8.1 POWER ON / OFF SEQUENCE

The following figures illustrate the recommended power ON and power OFF sequence of SSD1351 (assume V<sub>CI</sub> and V<sub>DDIO</sub> are at the same voltage level and internal  $V_{DD}$  is used).

## Power ON sequence:

- 1. Power ON  $V_{\text{CI}}$ ,  $V_{\text{DDIO}}$ .

- 2. After V<sub>CI</sub>, V<sub>DDIO</sub> become stable, set wait time at least 1ms (t<sub>0</sub>) for internal V<sub>DD</sub> become stable. Then set RES# pin LOW (logic low) for at least 2us (t<sub>1</sub>) (4) and then HIGH (logic high).

- 3. After set RÈS# pin ĽÓW (logic low), wait for at least 2us ( $t_2$ ). Then Power ON  $V_{\text{CC}}.^{(1)}$

- 4. After V<sub>CC</sub> become stable, send command AFh for display ON. SEG/COM will be ON after 200ms( $t_{AF}$ ).

## Power OFF sequence:

- 1. Send command AEh for display OFF. 2. Power OFF  $V_{CC}$ .

- 3. Wait for t<sub>OFF</sub>. Power OFF V<sub>CI</sub>, V<sub>DDIO</sub>. (where Minimum t<sub>OFF</sub>=80ms <sup>(3)</sup>, Typical  $t_{OFF}=100$ ms)

- (1) Since an ESD protection circuit is connected between VcI, VDDIO and Vcc, Vcc becomes lower than Vci whenever Vci, Vddio is ON and Vcc is OFF as shown in the dotted line of Vcc in above figures.

- (2) Vcc should be kept float (disable) when it is OFF.

- (3) VCI, VDDIO should not be Power OFF before Vcc Power OFF.

- (4) The register values are reset after t<sub>1</sub>.

- (5) Power pins (VDD, VCC) can never be pulled to ground under any circumstance.

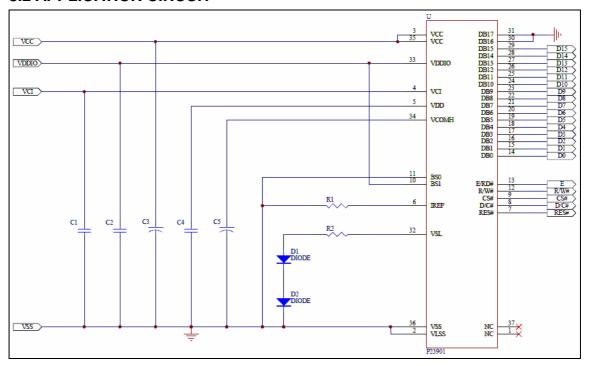

## **8.2 APPLICATION CIRCUIT**

## **Recommend components:**

C1, C2, C4: 1uF/16V(0805)

C3, C5: 4.7uF/35V (Tantalum type) or VISHAY (572D475X0025A2T)

R1: 1M ohm 1%(0603)

R2: 50 ohm 1/4W

D1, D2: RB480K(ROHM)

This circuit is for 8080 16bits interface

## 8.3 COMMAND TABLE

Refer to SSD1351 IC Spec.

## 9. RELIABILITY TEST CONDITIONS

| No. | Items                                  | Specification                                                                                            | Quantity |

|-----|----------------------------------------|----------------------------------------------------------------------------------------------------------|----------|

| 1   | High temp.<br>(Non-operation)          | 85℃, 240hrs                                                                                              | 5        |

| 2   | High temp. (Operation)                 | 70 ℃, 120hrs                                                                                             | 5        |

| 3   | Low temp. (Operation)                  | -40℃, 120hrs                                                                                             | 5        |

| 4   | High temp. / High humidity (Operation) | 65℃, 90%RH, 96hrs                                                                                        | 5        |

| 5   | Thermal shock (Non-operation)          | -40 °C ~85 °C (-40 °C /30min;<br>transit /3min; 85 °C /30min; transit<br>/3min) 1cycle: 66min, 20 cycles | 5        |

| 6   | Vibration                              | Frequency: 5~50HZ, 0.5G<br>Scan rate: 1 oct/min<br>Time: 2 hrs/axis<br>Test axis: X, Y, Z                | 1 Carton |

| 7   | Drop                                   | Height: 120cm<br>Sequence : 1 angle \ 3 edges and<br>6 faces<br>Cycles: 1                                | 1 Carton |

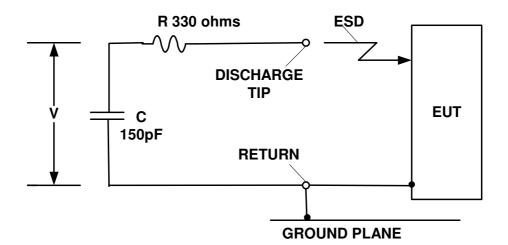

| 8   | ESD (Non-operation)                    | Air discharge model, ±8kV, 10 times                                                                      | 5        |

## Test and measurement conditions

- 1. All measurements shall not be started until the specimens attain to temperature stability.

- 2. All-pixels-on is used as operation test pattern.

- 3. The degradation of Polarizer are ignored for item 1, 4 & 5.

### **Evaluation criteria**

- 1. The function test is OK.

- 2. No observable defects.

- 3. Luminance: > 50% of initial value.

- 4. Current consumption: within  $\pm$  50% of initial value.

## 10. EXTERNAL DIMENSION

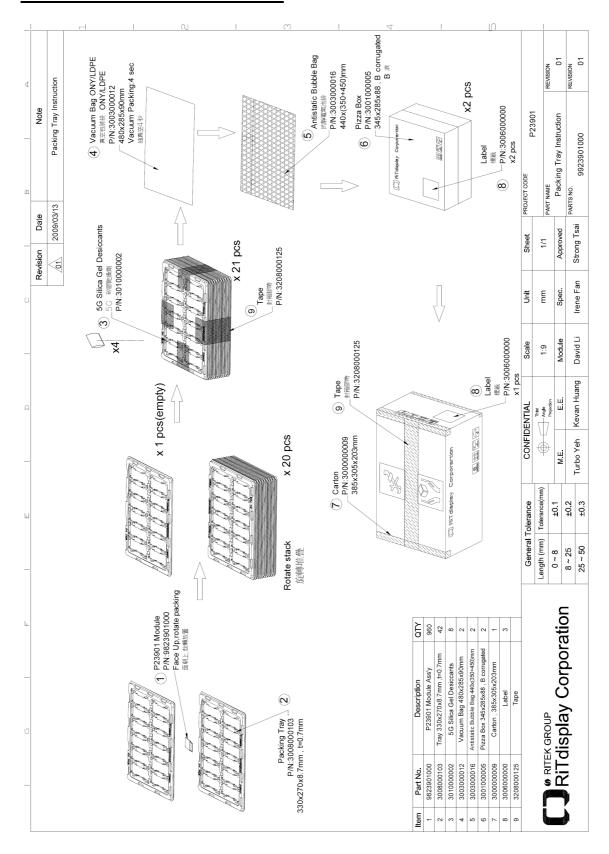

## 11. PACKING SPECIFICATION

- 17 - REV.: A03 2014/03/31

## 12. APPENDIXES

## **APPENDIX 1: DEFINITIONS**

## A. DEFINITION OF CHROMATICITY COORDINATE

The chromaticity coordinate is defined as the coordinate value on the CIE 1931 color chart for R, G, B, W.

## **B. DEFINITION OF CONTRAST RATIO**

The contrast ratio is defined as the following formula:

## C. DEFINITION OF RESPONSE TIME

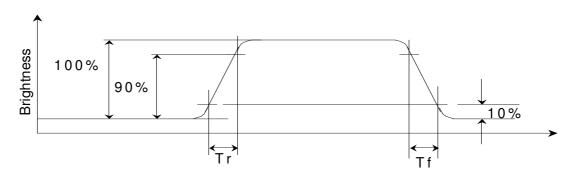

The definition of turn-on response time Tr is the time interval between a pixel reaching 10% of steady state luminance and 90% of steady state luminance. The definition of turn-off response time Tf is the time interval between a pixel reaching 90% of steady state luminance and 10% of steady state luminance. It is shown in Figure 2.

Figure 2: Response time

## D. DEFINITION OF VIEWING ANGLE

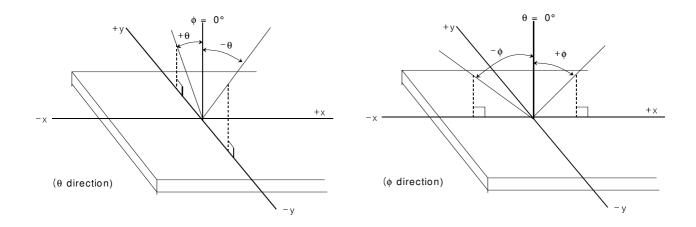

The viewing angle is defined as Figure 3. Horizontal and vertical (H & V) angles are determined for viewing directions where luminance varies by 50% of the perpendicular value.

Figure 3: Viewing Angle

## **APPENDIX 2: MEASUREMENT APPARATUS**

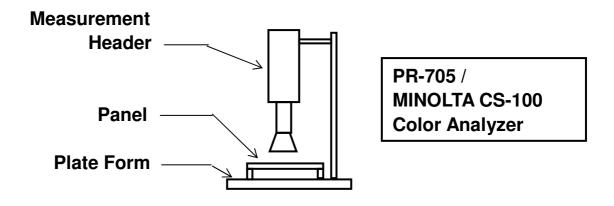

## A. LUMINANCE/COLOR COORDINATE

PHOTO RESEARCH PR-705, MINOLTA CS-100

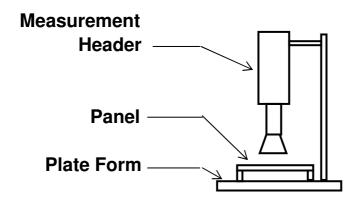

## **B. CONTRAST / RESPONSE TIME / VIEW ANGLE**

**WESTAR CORPORATION FPM-510**

Westar FPM-510

Display Contrast /

Response time /

View angle Analyzer

## C. ESD ON AIR DISCHARGE MODE

## **APPENDIX 3: PRECAUTIONS FOR USING THE OLED MODULE**

## Precautions for Handling

- 1. When handling the module, wear powder-free antistatic rubber finger cots, and be careful not to bend and twist it.

- 2. The OLED module is consisted of glass and film, and it should avoid pressure, strong impact, or being dropped from a high position.

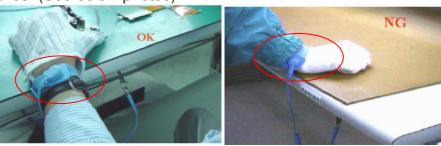

- 3. The OLED module is an electronic component and is subject to damage caused by Electro Static Discharge (ESD). And hence normal ESD precautions must be taken when handling it. Also, appropriate ESD protective environment must be administered and maintained in the production line. When handling and assembling the panel, wear an antistatic wrist strap with the alligator clip attached to the ground to prevent ESD damage on the panel. Also, ground the tools being used for panel assembly and make sure the working environment is not too dry to cause ESD problems. Antistatic wrist strap should touch human body directly instead of gloves. (See below photos).

- 4. Take out the panel one by one from the holding trays for assembly, and never put the panel on top of another one to avoid the scratch.

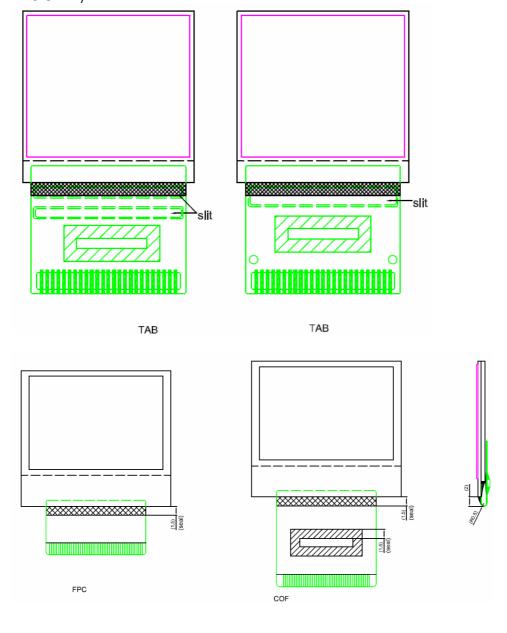

- 5. Avoid jerk and excessive bend on TAB/FPC/COF, and be careful not to let foreign matter or bezel damage the film.

- 6. When handling and assembling the module (panel + IC), grab the panel, not the TAB/FPC/COF.

- 7. Use the tweezers to open the clicks on the connector of PCB before the insertion of FPC/COF, and click them back in. Once the FPC/COF sits properly in the connector, use the tweezers to avoid the damages.

- 22 -

REV.: A03 2014/03/31

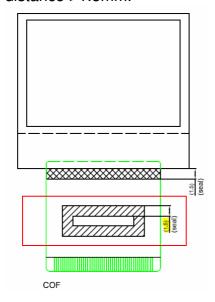

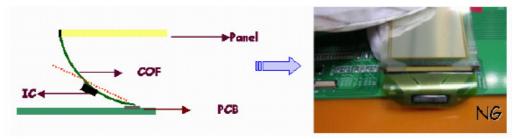

8. Please do not bend the film near the substrate glass. It could cause film peeling and TAB/FPC/COF damage. For TAB, It should bend the slit area as actual OLED it is. For FPC or COF, it is suggested to follow below pictures for instruction (distance between substrate glass and bending area >1.5mm; R>0.5mm).

- 23 - REV.: A03 2014/03/31

9. Avoid bending the film at IC bonding area. It could damage the IC ILB bonding. It should avoid bending the IC seal area. Please keep the bending distance >1.5mm.

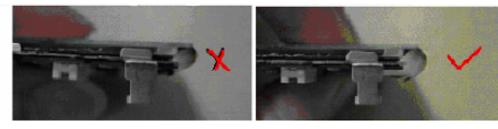

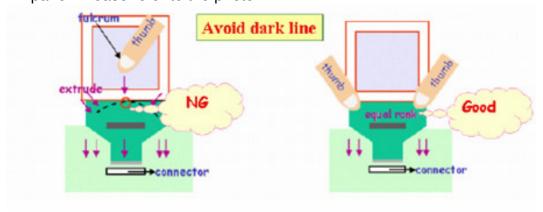

10. Use both thumbs to insert COF into the connector when assembling the panel. Please refer to the photo.

11. The working area for the panel should be kept clean. If the panel is accidentally dropped on the floor, do visual inspection of the panel first. Please use clean-room wiping cloth moistened with alcohol to wipe it off if dirt or grease stains the panel.

- 24 - REV.: A03 2014/03/31

- 12. Do not wipe the pin of film and polarizer with the dry or hard materials that will damage the surface. When cleaning the display surface, use the soft cloth with solvent, IPA or alcohol, to clean.

- 13. Protection film is applied to the surface of OLED panel to avoid the scratch. Please remove the protective film before assembling it. If the OLED panel has been stored for a long time, the residue adhesive material of the protective film may remain on the display surface after remove the protective film. Please use the soft cloth with solvent, IPA or alcohol, to clean.

- 14. When hand or hot-bar soldering TAB/FPC onto PCB, make sure the temperature and timing profiles to meet the requirements of soldering specification (the specification depends on the application or optimized by customer) to prevent the damage of IC pins by inappropriate soldering.

- 15. Solder residues arise from soldering process have to be cleaned up thoroughly before the module assembly.

- 16. Use the voltage and current settings listed in the specification to do the function test after the module assembly.

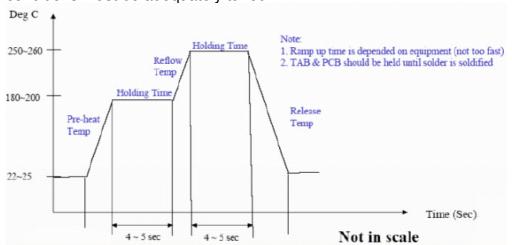

- 17. Suggestion for soldering process:

- i. TAB Lead- free soldering hot bar process

- 1. Use pulse heated bonding tool equipment

- 2. Material: Sn/Ag/Cu lead-free solder paste with typical 25um thickness on PCB pad. The TAB pin size and shape may be different, please base on the production line to adjust the thickness of PCB pad and temperature.

- 3. Bonding Force:--4kg per centimeter square as the starting point.

- 4. Suggested bonding tool temperature & time profile is as below for reference. Since there are differences in TAB soldering pins, soldering technicians' skills, mechanism...etc., the soldering conditions must be adequately tuned.

- 25 - REV.: A03 2014/03/31

- ii. TAB Lead- free soldering wire processIn case of manual soldering (Lead- free solder wire)

- 1. Solder wire contact iron directly: 280±5° at 3-5secs

- 2. Solder wire contact TAB lead directly (near iron but not contact): 380±5  $^{\circ}$ C, 3-5secs

- 3. Since there are differences in TAB soldering pins, soldering technicians' skills, mechanism...etc., the soldering conditions must be adequately tuned.

- iii. High temperature will result in rapid heat conduction to IC and might cause damage to IC, so please keep the temperature below 380  $^{\circ}$ C. Also, avoid damaging the polyimide and solder resist which might take place at high temperatures. Refold cycles base on the de-soldering status, if the plating of pin was damaged, it can not be used again.

- 26 - REV.: A03 2014/03/31

## Precautions for Electrical

## 1. Design using the settings in the specification

It is very important to design and operate the panel using the settings listed in the specification. It includes voltage, current, frame rate and duty cycle... etc. Operation the OLED outside the range of the specification should be entirely avoided to ensure proper operation of the OLED.

## 2. Maximum Ratings

To ensure the proper operation of the panel, never design the panel with parameters running over the maximum ratings listed in the specification. Also the logic voltages such as VIL and VIH have to be within the specified range in the specification to prevent any improper operation of the panel.

## 3. Power on/off procedure

To avoid any inadvertent effects resulting from inappropriate power on/off operations, please follow the directions of power on/off procedure on page 6. Any operation that does not comply with the procedure could cause permanent damage of the IC and should be avoided. When the logic power is not on, do not activate any input signal. Abrupt shutdown of power to the module, while the OLED panel is on, would cause OLED panel malfunction.

- 27 - REV.: A03 2014/03/31

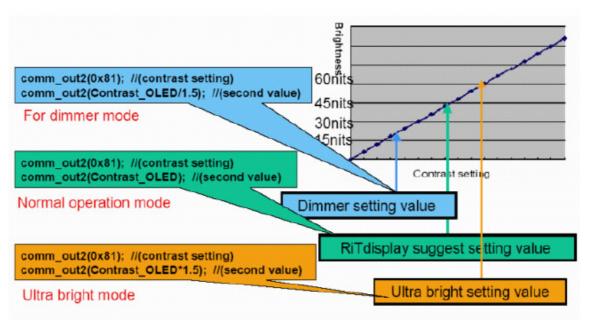

## 4. Power savings

To save power consumption of the OLED, please use partial display or sleep mode when the panel is not fully activated. Also, if possible, make the black background to save power.

The OLED is a self-luminous device and a particular pixel cluster or image can be lit on via software control. So power savings can be achieved by partial display or dimming down the luminance. Depending on the application, the user can choose among Ultra Bright Mode, Normal Operation Mode, and Sleeping Mode. The power consumption is almost in directly proportion to the brightness of the panel, and also in directly proportion to the number of pixels lit on the panel. The customer can save the power by the use of black background and sleeping mode. One benefit from using these design schemes is the extension of the OLED lifetime.

## 5. Adjusting the luminance of the panel

Although there are a couple of ways to adjust the luminance of the panel, it is strongly recommended that the customer change the contrast setting to adjust the luminance of the panel. Adjusting voltages to achieve desired luminance is not allowed. Be aware that the adjustment of luminance would accompany the change of lifetime of the panel and its power consumption as well.

## 6. Residual Image (Image Sticking)

The OLED is a self-emissive device. As with other self-emissive device or displays consisting of self-emissive pixels, when a static image frozen for a long period of time is changed to another one with all-pixels-on background, residual image or image sticking is noticed by the human eye. Image sticking is due to the luminance difference or contrast between the pixels that were previously turned on and the pixels that are newly turned on. Image sticking depends on the luminance decay curve of the display. The slower the decay, the less prominent the image sticking is. It is strongly recommended that the user employ the following three strategies to minimize image sticking.

- 28 - REV.: A03 2014/03/31

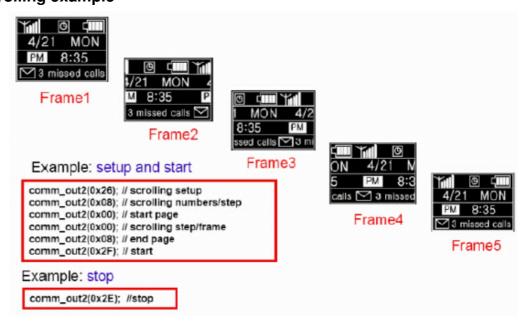

- 1. <u>Employ image scrolling or animation</u> to even out the lit-on time of each and every pixel on the display, also could use sleeping mode for reduced the residual image and extend the power capacity.

- 2. <u>Minimize the use of all-pixels-on or full white background</u> in their application because when the panel is turned on full white, the image sticking from previously shown patterns is the most revealing. Black background is the best for power savings, greatest visibility, eye appealing, and dazzling displays

- 3. If a static logo is used in the reliability test, change the pattern into its inverse (i.e., turn off the while pixels and turn on the previously unlit pixels) and freeze the inverse pattern as long as the original logo is used, so every pixel on the panel can be lit on for about the same time to minimize image sticking, caused by the differential turn-on time between the original and its reverse patterns.

## Scrolling example

- 29 - REV.: A03 2014/03/31

## Precautions for Mechanical

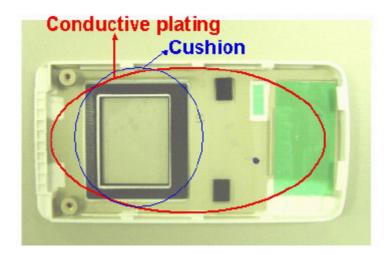

## 1. Cushion or Buffer tape on the cover glass

It is strongly recommended to have a cushion or buffer tape to apply on the panel backside and front side when assembling OLED panel into module to protect it from damage due to excessive extraneous forces.

It is recommended that a plating conductive layer be used in the housing for EMI/EMC protection. And, the enough space should be reserved for the IC placement if the IC thickness is thicker than the TAB film when customer design the PCB.

# 2. Avoid excessive bending of film when handling or designing the panel into the product

The bending of TAB/COF/FPC has to follow the precautions indicated in the specification, extra bending or excessive extraneous forces should be avoided to minimize the chances of film damage. If bending the film is necessary, please bend the designated bending area only. Please refer to items 8 and 9 of Precautions for Handling for more information.

## Precautions for Storage and Reliability Test

## 1. Storage

Store the packed cartons or packages at  $25^{\circ}\text{C} \pm 5^{\circ}\text{C}$ ,  $55\% \pm 10\%$ RH. Do not store the OLED module under direct sunlight or UV light. For best panel performance, unpack the cartons and start the production of the panels within six months after the reception of them.

## 2. Reliability Test

RiTdisplay only guarantees the reliability of the OLEDs under the test conditions and durations listed in the specification.