# EVERLIGHT

# DATASHEET

# Dual-Channel Isolated Gate Driver CE21550X-G Series

## Features:

- Compliance Halogens Free

- (Br < 900 ppm, Cl < 900 ppm, Br+Cl < 1500 ppm)

- 3V to 5.5V Input VCCI Range to Interface with Both Digital and Analog Controllers

- Up to 25V VDD Output Drive Supply

- Programmable Overlap and Dead Time

- Wide temperature range: -40°C to 125°C

# Description

The CE21550X has a source peak current of 4A and a sink peak current of 8A. The maximum switching frequency can reach 5MHz. It is suitable for gate driver of MOSFET, IGBT and SiC MOSFET.

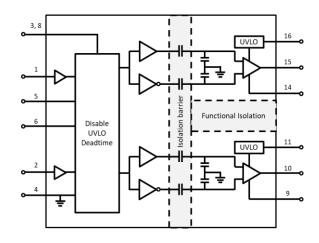

Every driver can be configured as two low-side drivers, two high-side drivers, or a half-bridge driver with programmable dead time (DT). A DISABLE pin shuts down both outputs simultaneously when it is set high and allows normal operation when left open or grounded. As a fail-safe measure, primary-side logic failures force both outputs low.

# **Applications**

- HEV and BEV Battery Chargers

- Isolated Converters in DC-DC and AC-DC Power Supplies

- · Server, Telecom, IT, and Industrial Infrastructures

- Motor Drive and DC-AC Solar Inverters

- LED Lighting

- Inductive Heating

- Uninterruptible Power Supply (UPS)

# **Pin Description**

|                                 |                      |               | Pin  | Symbol                              | Description                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------|----------------------|---------------|------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 INA<br>2 INB                  | VDDA<br>OUTA         | 16<br>15      | 1    | INA                                 | Input signal for A channel.<br>INA input has a TTL/CMOS compatible input threshold. This<br>pin is pulled low internally if left open. It is recommended to<br>tie this pin to ground if not used to achieve better noise<br>immunity.                                                                                                                         |

| 3 VCC1<br>4 GND                 |                      |               | 2    | INB                                 | Input signal for B channel.<br>INB input has a TTL/CMOS compatible input threshold. This<br>pin is pulled low internally if left open. It is recommended to<br>tie this pin to ground if not used to achieve better noise<br>immunity.                                                                                                                         |

|                                 |                      |               | 3,8  | VCC1                                | Primary-side supply voltage.                                                                                                                                                                                                                                                                                                                                   |

| 5 DISABLE                       |                      |               | 4    | GND                                 | Primary-side ground reference.                                                                                                                                                                                                                                                                                                                                 |

| 6 DT<br>7 NC<br>8 VCC1          | VDDB<br>OUTB<br>VSSB | 11<br>10<br>9 | 5    | DISABLE                             | Disables both driver outputs if asserted high, enables if set<br>low or left open.<br>This pin is pulled low internally if left open. If this pin is not<br>used, it is recommended to ground this pin to obtain better<br>noise immunity. When connecting to a microcontroller, use a<br>low ESR/ESL capacitor of approximately 1nF to bypass the<br>DIS pin. |

| 0.1μF capacitor<br>GND.         |                      | <b> </b> 1    | 6    | DT                                  | Programmable dead time function.<br>Tying DT to VCCI allows the outputs to overlap. Leaving DT open sets, the dead time to <15 ns. Placing a $500\Omega$ to $500k\Omega$ resistor (RDT) between DT and GND adjusts dead time according to: DT(ns) $\approx$ 10 x RDT(k $\Omega$ ).                                                                             |

| 1µF capacitor f<br>VDDB to VSSA |                      |               | 7    | NC                                  | No connection.                                                                                                                                                                                                                                                                                                                                                 |

|                                 |                      |               | 9    | VSSB                                | Ground for secondary-side driver B.                                                                                                                                                                                                                                                                                                                            |

|                                 |                      | 10            | OUTB | Output of driver B.                 |                                                                                                                                                                                                                                                                                                                                                                |

|                                 |                      | 11            | VDDB | Secondary-side power for driver B.  |                                                                                                                                                                                                                                                                                                                                                                |

|                                 |                      | 14            | VSSA | Ground for secondary-side driver A. |                                                                                                                                                                                                                                                                                                                                                                |

|                                 |                      | 15            | OUTA | Output of driver A.                 |                                                                                                                                                                                                                                                                                                                                                                |

|                                 |                      |               | 16   | VDDA                                | Secondary-side power for driver A.                                                                                                                                                                                                                                                                                                                             |

# Absolute Maximum Ratings (Ta=25°C)

| Parameter                | Symbol           | Rating               | Unit  |

|--------------------------|------------------|----------------------|-------|

| Supply voltage           | V <sub>CC1</sub> | 7                    | V     |

| Input signal voltage     | V <sub>IN</sub>  | Vcc1+0.5             | V     |

| Driver bias supply       | Vdd              | 30                   | V     |

| Maximum Output Voltage   | V <sub>OUT</sub> | V <sub>DD</sub> +0.5 | V     |

| Isolation Voltage *1     | V <sub>ISO</sub> | 5000                 | V rms |

| Operating Temperature    | T <sub>OPR</sub> | -40 ~ +125           | °C    |

| Storage Temperature      | T <sub>STG</sub> | -55 ~ +150           | °C    |

| Soldering Temperature *2 | T <sub>SOL</sub> | 260                  | °C    |

#### Notes:

\*1 AC for 1 minute, R.H.= 40 ~ 60% R.H. In this test, pins 1 to 8 are shorted together, and pins 9 to 16 are shorted together.

\*2 For 10 seconds.

\*3 Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# **Recommended Operating Conditions**

| Parameter             |          | Symbol            | Min | Max              | Unit |

|-----------------------|----------|-------------------|-----|------------------|------|

| Input Supply Voltage  |          | V <sub>CC1</sub>  | 3   | 5.5              | V    |

|                       | CE21550A |                   | 6.5 | 25               | V    |

| Output Supply Voltage | CE21550B | V <sub>DD</sub> - | 9.2 | 25               | V    |

| Input voltage         |          | V <sub>IN</sub>   | 0   | V <sub>CC1</sub> | V    |

| Output voltage        |          | Vo                | 0   | V <sub>DD</sub>  | V    |

# **Electro-Optical Characteristics**

| Parameter                          | Symbol                       | Min  | Тур.                    | Max.   | Unit | Condition                                             |

|------------------------------------|------------------------------|------|-------------------------|--------|------|-------------------------------------------------------|

|                                    | Ivccı                        |      | 0.5                     | 1.1    | mA   | $V_{INX} = 0V$                                        |

| Quiescent Current                  | Ivddx                        |      | 0.9                     | 1.5    | mA   | V <sub>INX</sub> = 0V                                 |

|                                    | Ivcci                        |      | 0.9                     |        | mA   | V <sub>INX</sub> f=500kHz, 50% duty                   |

| Operating Current                  | Ivddx                        |      | 2.2                     |        | mA   | cycle                                                 |

| UVLO Rising<br>Threshold           | V <sub>VCCI_ON</sub>         | 2.55 | 2.7                     | 2.85   | V    |                                                       |

| UVLO Falling<br>threshold          | Vvcci_off                    | 2.35 | 2.5                     | 2.65   | V    |                                                       |

| Threshold hysteresis               | Vvcci_hys                    |      | 0.2                     |        | V    |                                                       |

| UVLO Rising threshold              | $V_{VDDX\_ON}$               | 5.7  | 6.1                     | 6.5    | V    |                                                       |

| UVLO Falling<br>threshold          | Vvddx_off                    | 5.4  | 5.8                     | 6.2    | V    | <br>CE21550A                                          |

| UVLO Threshold<br>hysteresis       | V <sub>VDDX_HYS</sub>        |      | 0.3                     |        | V    | _                                                     |

| UVLO Rising threshold              | Vvddx_on                     | 8.3  | 8.7                     | 9.2    | V    |                                                       |

| UVLO Falling<br>threshold          | Vvddx_off                    | 7.8  | 8.2                     | 8.7    | V    | CE21550B                                              |

| UVLO Threshold<br>hysteresis       | Vvddx_hys                    |      | 0.5                     |        | V    |                                                       |

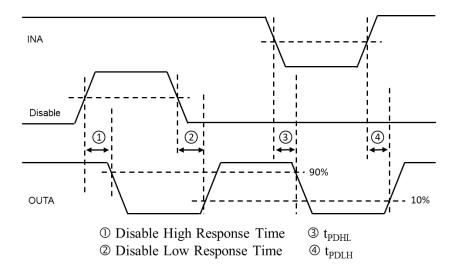

| Input high threshold voltage       | V <sub>INX_H</sub><br>Vdis_h | 1.6  | 1.8                     | 2      | V    |                                                       |

| Input low threshold voltage        | V <sub>INX_L</sub><br>Vdis_l | 0.8  | 1                       | 1.2    | V    |                                                       |

| Input threshold<br>hysteresis      | Vinx_hys<br>Vdis_hys         |      | 0.8                     |        | V    |                                                       |

| Peak output source current         | lo+                          |      | 4                       |        | А    | $C_{VDD} = 10\mu F,$<br>$C_{LOAD} = 0.68\mu F,$       |

| Peak output sink current           | lo-                          |      | 8                       |        | А    | f = 100Hz, bench<br>measurement                       |

| Output resistance at<br>high state | Rон                          |      | 1                       |        | Ω    | I <sub>OUT</sub> = -10 mA                             |

| Output resistance at low state     | Rol                          |      | 0.4                     |        | Ω    | I <sub>OUT</sub> = 10 mA                              |

| Output voltage at high state       | V <sub>OH</sub>              |      | 11.99                   |        | V    | V <sub>DDX</sub> = 12 V,<br>I <sub>OUT</sub> = -10 mA |

| Output voltage at low state        | Vol                          |      | 4                       |        | mV   | $V_{DDX} = 12 V,$<br>$I_{OUT} = 10 mA$                |

|                                    |                              | Over | lap determir<br>INA INB | ned by | ns   | Pull DT pin to VCCI                                   |

| Dead time                          | DT                           | 0    | 8                       | 15     | ns   | DT pin is left open                                   |

|                                    |                              | 150  | 200                     | 250    | ns   | R <sub>DT</sub> = 20 KΩ                               |

$V_{CC1} = 3.3V$  or 5V,  $T_A = 25^{\circ}C$ ,  $V_{DDA} = V_{DDB} = 12$  V, unless otherwise noted.

| Parameter                                              | Symbol             | Min | Тур. | Max. | Unit  | Condition                                    |

|--------------------------------------------------------|--------------------|-----|------|------|-------|----------------------------------------------|

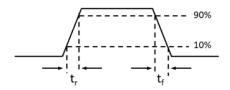

| Output rise time                                       | tr                 |     | 7    | 18   | ns    | $C_{OUT} = 1.8 nF$                           |

| Output fall time                                       | t <sub>f</sub>     |     | 8    | 12   | ns    | C <sub>OUT</sub> = 1.8nF                     |

| Minimum pulse width                                    | t <sub>PWmin</sub> |     | 10   | 20   | ns    | Output off for less than minimum, Cout = 0pF |

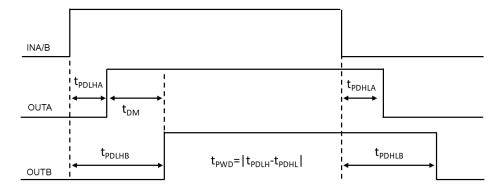

| Propagation delay<br>Low to High                       | <b>t</b> PDHL      | 14  | 19   | 30   | ns    |                                              |

| Propagation delay<br>High to Low                       | <b>t</b> PDLH      | 14  | 19   | 30   | ns    |                                              |

| Pulse width distortion                                 | <b>t</b> PWD       |     |      | 5    | ns    |                                              |

| Propagation delays<br>matching between<br>Vouta, Voutb | tом                |     |      | 5    | ns    | f = 100kHz                                   |

| High-level<br>common-mode<br>transient immunity        | CM <sub>H</sub>    |     | 100  |      | kV/us | V <sub>CM</sub> =1000V;                      |

| Low-level<br>common-mode<br>transient immunity         | CM∟                |     | 100  |      | kV/us | V <sub>CM</sub> =1000V;                      |

$V_{CC1}$  = 3.3V or 5V, T<sub>A</sub>=25°C,  $V_{DDA}$  =  $V_{DDB}$  = 12 V, unless otherwise noted.

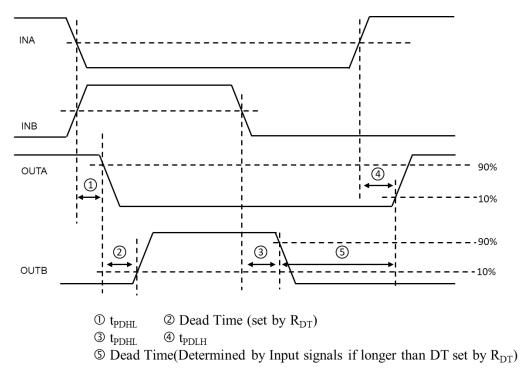

# Fig. 1 Overlapping inputs, Dead Time Disable

shows how to calculate pulse width distortion( $t_{PWD}$ ) and delay matching ( $t_{DM}$ ) from the propagation delays of channels A and B. It can be measured by ensuring that both inputs are in phase and disabling the dead time function by shorting the DT Pin to  $V_{CC1}$ .

# **Fig.2 Rising and Falling Time**

# Fig.3 Input and Disable Response Time

# Fig.4 Programmable Dead Time

Leaving the DT pin open or tying it to GND through an appropriate resistor (RDT) sets a dead-time interval.

# **Order Information**

#### Part Number

# CE21550X(TA)-G

## Note

| CE    | = | denotes EVERLIGHT |

|-------|---|-------------------|

| 21550 | = | part no.          |

| Х     | = | VDD Supply Min.   |

|       |   | A: 6.5V           |

|       |   | B: 9.2V           |

| G     | = | Halogens free     |

|       |   |                   |

| Option | Description                                     | Packing quantity    |

|--------|-------------------------------------------------|---------------------|

| (TA)   | Surface mount lead form + TA tape & reel option | 1500 units per reel |

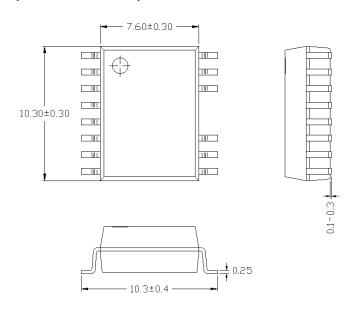

## Package Dimension (Dimensions in mm)

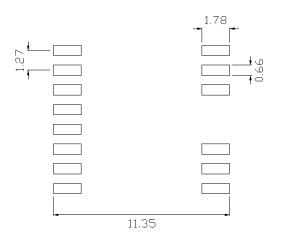

# Recommended pad layout for surface mount leadform

Notes.

Suggested pad dimension is just for reference only. Please modify the pad dimension based on individual need.

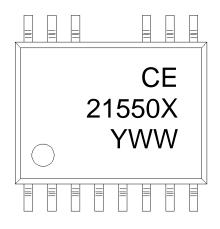

# **Device Marking**

#### Notes

| CE     | denotes EVERLIGHT         |

|--------|---------------------------|

| 21550X | denotes Device Number     |

| Y      | denotes 1 digit Year code |

| WW     | denotes 2 digit Week code |

Reference: IPC/JEDEC J-STD-020D

# **Precautions for Use**

## 1. Soldering Condition

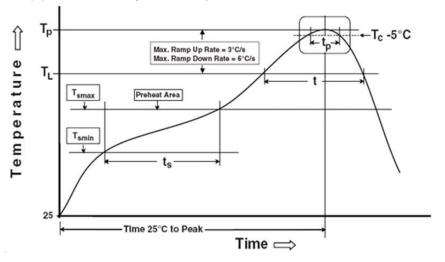

1.1 (A) Maximum Body Case Temperature Profile for evaluation of Reflow Profile

Note:

#### Preheat

| Temperature min (T <sub>smin</sub> )                      | 150 °C           |

|-----------------------------------------------------------|------------------|

| Temperature max (T <sub>smax</sub> )                      | 200°C            |

| Time ( $T_{smin}$ to $T_{smax}$ ) ( $t_s$ )               | 60-120 seconds   |

| Average ramp-up rate $(T_{smax} to T_p)$                  | 3 °C/second max  |

| Other                                                     |                  |

| Liquidus Temperature (T <sub>L</sub> )                    | 217 °C           |

| Time above Liquidus Temperature (t ∟)                     | 60-100 sec       |

| Peak Temperature (T <sub>P</sub> )                        | 260°C            |

| Time within 5 °C of Actual Peak Temperature: $T_{P}$ -5°C | 30 s             |

| Ramp- Down Rate from Peak Temperature                     | 6°C /second max. |

| Time 25°C to peak temperature                             | 8 minutes max.   |

| Reflow times                                              | 3 times          |

# DISCLAIMER

- 1. Above specification may be changed without notice. EVERLIGHT will reserve authority on material change for above specification.

- 2. The graphs shown in this datasheet are representing typical data only and do not show guaranteed values.

- 3. When using this product, please observe the absolute maximum ratings and the instructions for use outlined in these specification sheets. EVERLIGHT assumes no responsibility for any damage resulting from use of the product which does not comply with the absolute maximum ratings and the instructions included in these specification sheets.

- 4. These specification sheets include materials protected under copyright of EVERLIGHT. Reproduction in any form is prohibited without the specific consent of EVERLIGHT.

- 5. This product is not intended to be used for military, aircraft, automotive, medical, life sustaining or life saving applications or any other application which can result in human injury or death. Please contact authorized Everlight sales agent for special application request.

- 6. Statements regarding the suitability of products for certain types of applications are based on Everlight's knowledge of typical requirements that are often placed on Everlight products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and/or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Everlight's terms and conditions of purchase, including but not limited to the warranty expressed therein.